The SAS4 standard incorporates a Reed-Solomon (RS) forward error-correction (FEC) code. Other standards such as cache coherent interconnect for accelerators (CCIX) are also considering FEC for next-generation high-speed serial communication systems requiring low error rate over high loss channels. Both serial attached SCSI (SAS) and CCIX systems require link latency below 100ns, which severely constrains the choice of code and design of decoder. In this paper, we study error characteristics at the receiver for various SAS4 channels. We evaluate the performance of several choices of RS code and show how a frame-interleaved RS(30,26) code can achieve 1e-15 bit-error rate (BER) in the presence of burst errors. Furthermore, we studied the impact of 128/130 encoding scheme for a high insertion loss channel.

The SAS 24G standard specifies an insertion loss of 30 dB [1]. In order to achieve the target bit error rate (BER) of 1e-15, forward error correcting (FEC) codes are considered. However, the SAS protocol relies on very low latency, which disqualifies most FEC codes currently deployed in networking applications.

Over such a lossy channel it is very difficult to achieve the target BER of 1e-15 relying solely on pre-emphasis and decision feedback equalization [2][3]. Employing FEC is a natural solution to achieve the desired BER in SAS4 channels [4][5]. The aim is to achieve 1e-15 BER after FEC when the raw BER without FEC reaches 1e-6. At the same time the FEC must meet limits on acceptable power and latency increase.

Figure 1 shows the equalized pulse response of a typical long SAS4 channel, released by EMC to the SAS4 committee in August 2016. This channel has a large H1 value, which will lead to significant decision feedback equalization (DFE) error propagation. We use this EMC long channel in our initial SAS4 FEC study.

Both encoding and decoding of a FEC will introduce latency. The latency associated with decoding is often significant [6]-[10]. The RS(30, 26) FEC selected by the SAS4 committee minimizes this latency impact because the data frame is short and because the error locations can be found directly, without the need for a Chien search.

The facts of the initial SAS4 RS FEC in our study:

- 128b/130b encoding is used instead of 8b/10b SAS3 encoding, added 01 or 10 to 128 data bits

- FEC is using RS (30, 26), T=2, 5-bit/symbol

- Data rate is 22.5 Gbit/s based on doubling SAS3 data rate of 12 Gbit/s with 8b/10b encoding

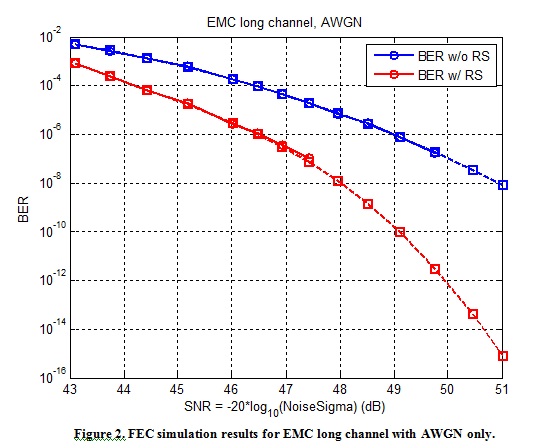

Figure 2 shows the FEC simulation results for EMC long channel with additive white Gaussian noise (AWGN) only. With raw BER 1e-6, we can only achieve 1e-10 after the single RS (30, 26) FEC code above. And we need around 1e-8 raw BER to achieve 1e-15 after FEC. The dash-line parts in the plot are extrapolated data.

To improve FEC performance in order to achieve 1e-15 after FEC at raw BER 1e-6, we studied two possible solutions:

- FEC with larger frame size and stronger error correction capability;

- Use frame interleave scheme to break long burst error.

Figures 3 and 4 show two additional examples of the channel pulse response in a SAS storage system. These measurements were released by HPE to the SAS4 committee in August, 2016 and represent typical short and long reach applications. Please note that HP short channel has a very small H1 value, while HP long channel has a large H1 value. Figure 5 shows the frequency domain insertion loss characteristic for the three typical SAS4 channels studied in this paper.